ハードウェア・ソフトウェア協調設計班では,あるアプリケーションに特化した命令セットを持つ

プロセッサのハードウェア・ソフトウェア協調設計を行っています.

現在は「Packed SIMD型命令を持つプロセッサを対象としたハードウェア・ソフトウェア協調設計システム SPADES」

というハードウェア・ソフトウェア協調設計システムの研究を行っています.

プロセッサとは,ある応用プログラム(アプリケーション)を記述した命令が入力されたときに,その指示にしたがって所定のデータ処理動作を実行する半導体回路を指します.「LSI」という単語を思い浮かべてもらえば,だいたいイメージは合っています

(厳密には異なるものを指します).

プロセッサは,我々が普段の生活で使うほとんどのものに組み込まれています.一番特徴的なのはケータイやパソコンなど,多くの信号処理を必要とする電気製品です.プロセッサを設計する際に目指すべきことは,処理速度がより速く,プロセッサ面積がより小さくなるような構成方法を見つけることです.プロセッサはHWとSWの組み合わせによって構成されます.

あるデータに対する複雑な処理動作があった場合に,プロセッサから一言指示を出せば処理を実行して結果を返してくれるような専用演算器の仕組みを指します.一般にHWを使用する場合,処理に必要な時間は短時間で済みますが,プロセッサ全体の面積は大きくなってしまいます.

あるデータに対する複雑な処理動作があった場合に,単純な作業のみ実行可能な演算器をいくつか動員し,それぞれの演算器に指示を出しながら各自の処理を順番に実行し,結果を出す仕組みを指します.一般にSWを使用する場合,プロセッサ全体の面積は小さくて済みますが,処理に必要とする時間は長くなってしまいます.

ハードウェアとは,ある命令の専用器のことで,その命令を実行する処理時間は短くてすみますが,かわりに面積を食ってしまいます.逆に,ソフトウェアとは,ある命令を単純な作業のみ実行可能な演算器をいくつか動員し実行させるため,その命令を実行する処理時間は長くなってしまうが,面積は食いません.このように,プロセッサを構成する際に使用するHWとSWの組み合わせを変えることによって,異なる構成のプロセッサが出来上がります.HW部品を多く使用すれば,処理時間は短くなりますがその分プロセッサの面積は大きくなってしまいます.逆にSW部品を多く使用すれば,プロセッサ面積は小さく抑えられますがその分処理時間は長くなってしまいます.このように「面積を取れば,時間は捨てないといけない.逆に時間を取れば,面積は捨てないといけない.」といった性質のことをトレードオフといいます.

ハードウェア・ソフトウェア協調設計システムとは,このようなトレードオフの関係があるハードウェアとソフトウェアの組合せをさまざまな制約を気にしながら決定し,あるアプリケーションに特化したプロセッサを自動的に生成することを目的としたシステムです.

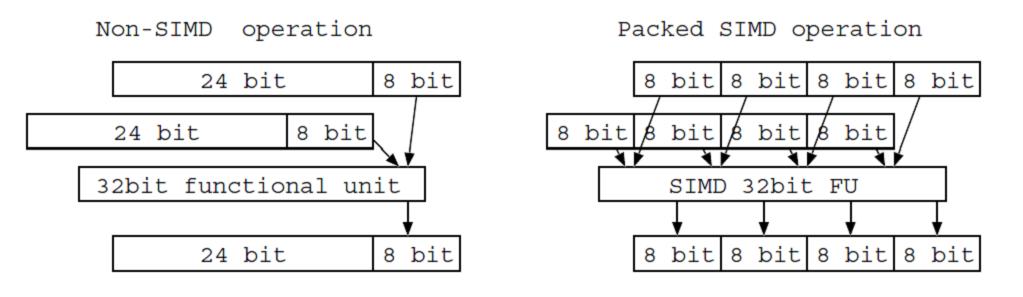

Packed SIMD型命令とは,1つのbビット演算ユニットを用いて,n個のb/nビット演算を実行させるものです.ここでnのことを梱包数と呼びます.例えば,32ビットのPacked SIMD型演算ユニットを用いた場合,4個の8ビット演算を同時に実行できること(4梱包演算)ができるので,通常の32ビット演算器を用いて4個の8ビット演算を個々に実行するよりも4倍の速さで演算ができるようになります.

|

我々が対象としているPacked SIMD型命令には,さまざまな種類が存在します.例えば,演算する梱包数を選択できたり,演算し終えた後のシフトの有無,およびシフト有りの場合にはそのシフトの方向とシフト量をそれぞれ選択することができます.選択することができる演算の種類を下表に示します.

| 演算の種類 | 加算・減算・乗算・乗加算 |

| 梱包数 | 1梱包・2梱包・4梱包 |

| ビット拡張 | ビット拡張の有無.上位ビットor下位ビットの演算の選択 |

| 符号ビット | 符号ビット付き演算or符号ビットなし演算の選択 |

| シフト | シフトの有無・シフトの方向(右,左)・シフトの量(1~32) |

| 飽和演算 | 飽和演算の有無 |

例えば,「4梱包,ビット拡張なし,符号ビットなし,右に4シフト,飽和演算なし」の乗算命令(Mul_4_ur4w)もあれば,「2梱包,ビット拡張あり,上位ビット演算,符号ビットあり,シフトなし,飽和演算あり」の加算命令(ADD_2h_ss)もあります.このように,Packed SIMD型命令には何通りもの命令の種類が存在します.

ここで,Packed SIMD型命令について「8ビット演算を4並列にやるだけならば, 32ビット演算器を使うのではなく, 8ビット演算器を4つ使えばいいじゃん」と思った人もいると思います.しかし,我々の対象としているPacked SIMD型演算器というものは,「4梱包もできてなおかつ1梱包演算も実行できる」といった構成をとることもできます.こうすることによって,8ビット演算を4並列でしたい場合に,あまってる32ビット演算器を用いて計算することが可能になり,結果としてプロセッサの面積を減少させることができるようになります.

ハードウェア・ソフトウェア協調設計システムの役割を果たすためには,次の作業が必要です.

我々のシステムであるSPADESは,以上のような作業を行うために以下に示す4つの処理系によって成り立っています.

協調合成システムの入力となる「アプリケーションのC言語記述ファイル」を解析し,最速実行可能アセンブリコードを生成します. アプリケーション解析処理によって得られた「最速実行可能アセンブリコード」を HW/SW分割系に向けて出力します.

コンパイラ系から出力される「最速実行可能アセンブリコード」をもとに,プロセッサ面積およびアプリケーションの実行時間を見積もりながらプロセッサのハードウェア構成を決定します.同時に,得られたプロセッサ構成で実行可能となるようにアセンブリコードを変更します.分割処理によって得られた「プロセッサのハードウェア構成」および「変更済みアセンブリコード」をハードウェア生成系とソフトウェア生成系に向けて出力します.

HW/SW分割系から出力される「プロセッサのハードウェア構成」をもとに,プロセッサのHDL記述を生成します. ハードウェア生成系から出力されるプロセッサのHDL記述が,協調合成システム全体における出力の一つとなります.

HW/SW分割系から出力される「プロセッサのハードウェア構成」および「変更済みアセンブリコード」をもとに,合成されるプロセッサ向けのソフトウェア環境を生成します.ソフトウェア環境とはコンパイラ,アセンブラおよびシミュレータを指します. ソフトウェア生成系から出力されるソフトウェア環境が,協調合成システム全体における出力の一つとなります.

また,SPADESの入力と出力は次のようになっています.

入力

出力

なお,SPADESでは,「実行時間制約を満たす中で最小面積のあるアプリケーションに特化したプロセッサ」を生成することを目的としています.そのために,入力に「アプリケーションの実行時間制約」をいれることが必要になります.

システムをSWで実装する場合,処理の内容を記述したプログラムをメモリに保存しておくことが必要となります.しかし,メモリはプロセッサに比べてアクセス速度が非常に遅いため,メモリからデータを取ってくる間にプロセッサがそれを待つことになってしまいます.そのため,システム全体としての処理速度が長くなってしまいます.

そこで,よく使うデータだけをプロセッサに近い位置(あるいは内部)にある高速なメモリに入れておき,アクセス時間を短くしようという考えが提案されました.それがキャッシュメモリです.キャッシュメモリにはデータの置き方によって,以下のような3つの構成があります.

こうした構成は,データへのアクセス時間やほしいデータがキャッシュ上にある確率(ヒット率といいます)がそれぞれ異なるため,一概にどれがよいとは断言できません.あるアプリケーションAではダイレクトマップ方式がよくても,違うアプリケーションBではセットアソシアティブ方式がよい場合もあるのです.また,キャッシュの容量やラインサイズ(メインメモリから1度に持ってくるデータ量をこのようにいいます)も同じようにアプリケーションによって最適な構成は異なってきます.容量が大きなメモリは面積が大きくなり,アクセス時間も探索するデータ量が大きくなってしまうために長くなります.逆に小さいとキャッシュにおけるデータ量が小さくなるため,ヒット率が下がってしまいます.さらに,ラインサイズが大きいと,一度に多くのデータをもってくることができますが,メインメモリからデータを持ってくる時間が長くなってしまいます.逆に小さいと何度もデータを持ってこなければならなくなる可能性があります.

キャッシュ最適化とは,アプリケーションの内容を解析し,こうした要素を調整することで,それに適した構成を出力することを目標としたシステムです.これによって,SWで行う処理に関してもある程度の高速化を実現することができます.